今天给大伙讲解一下关于工作和学习中常用的各种类型封装的设计技巧以及注意事项

【关于封装的设计】

方法1. 手动制作

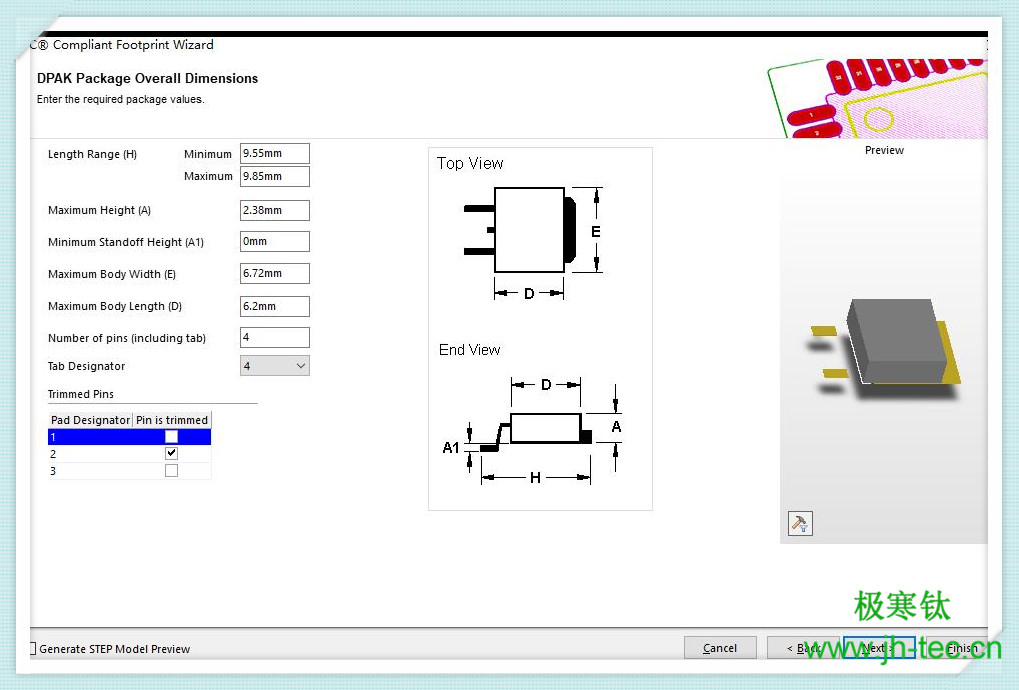

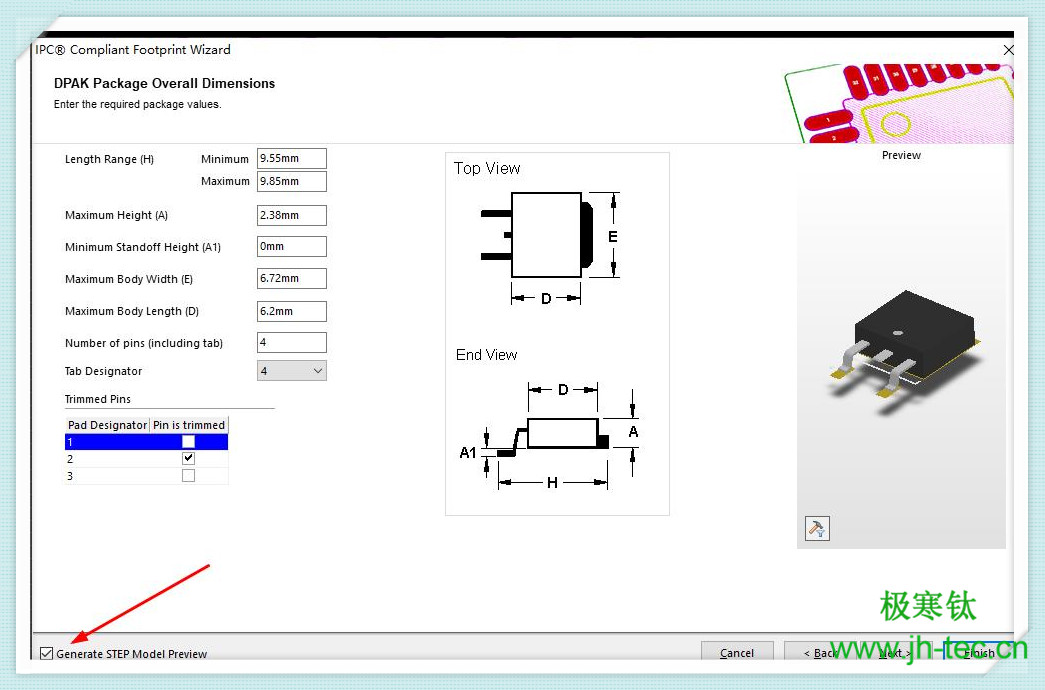

手动制作的方法可以是自己见一个新的元器件,然后根据手册上的参数表自己设计每个焊盘及间距,这个不多讲,基本功;另外一种方式就是通过封装导向来完成,这里提一点,在AD软件16版本之后有一个生成STEP模型的选项,非常的好,但很多朋友可能没有注意到这个功能,如下图所示:

方法2. 利用软件获取

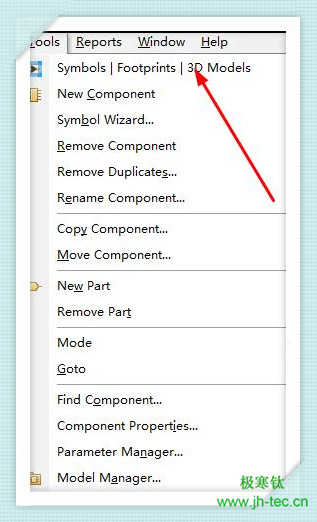

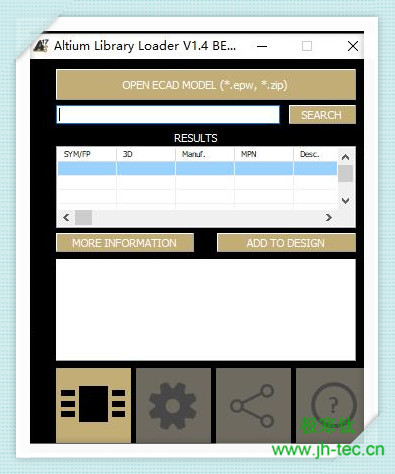

下面推荐一个针对AD软件可自动获取封装的方式,https://componentsearchengine.com/pcb-libraries.php 通过这个网站下载好插件,目前该插件仅支持AD17版及以上版本。安装好之后,打开AD软件的Tools选择如下,可看到右边的界面,注册登录账号,然后设置相应的库保存路径,即可在上面搜索常用的厂商器件型号!非常方便,但是需要注意的是,该方式生成的封装会存在一些问题,比如管脚的宽度、长度等尺寸问题以及间隙大小,建议自己再次核对之后再使用。

题外话:该软件的之前还有个BUG,生成的封装一但对焊盘使用查找相似对象功能,立刻就会使整个AD软件卡死甚至奔溃,后来我发邮件给了制作者说明,没想到他们一周之后竟然回复我,已完善bug,并让我帮助他们测试新版本~ 感叹一下国外这种机构做事情还是挺高效的。

方法3, 各个网站获取

目前很多网站都有可下载封装的渠道,下面推荐一个AD官网常用器件的库,https://designcontent.live.altium.com/ 该网站可以获取很多大厂的器件库,钛叔之前也去下载过,不过发现部分器件存在一些问题,大家在使用过程中一定要慎重核实。

另外再推荐一个网站 https://www.3dcontentcentral.cn/ 该网站主要用于平时下载3D模型,非常好用。

小结,无论哪种方式,都一定要经过验证再投入量产使用,要注意细节,有时候一个细小的设计差错可能给后期量产带来灾难性的的后果

【详细讲设计封装的细节】

1.关于封装焊盘的大小

焊盘多大合适,焊盘太大,SMT锡膏太多会产生大量锡珠,芯片管脚容易短路;焊盘太小,锡膏不够,易虚焊;当然合适最好,如何合适? 参考芯片手册,略大于引脚,切忌不要因为方便手工焊接而设计的过于长或宽,如果纯粹是手工焊接就无所谓,如果后期设计量产,这可能带来巨大的风险(其实无论是手工焊接还是SMT,都建议严格按照此标准来设计)。

2.焊盘大小对称的重要性

如果焊盘大小不对称,会出现什么问题呢——立碑曼哈顿现象,在回流焊接贴片元器件的过程中,一端焊接在焊盘上,另一端翘立

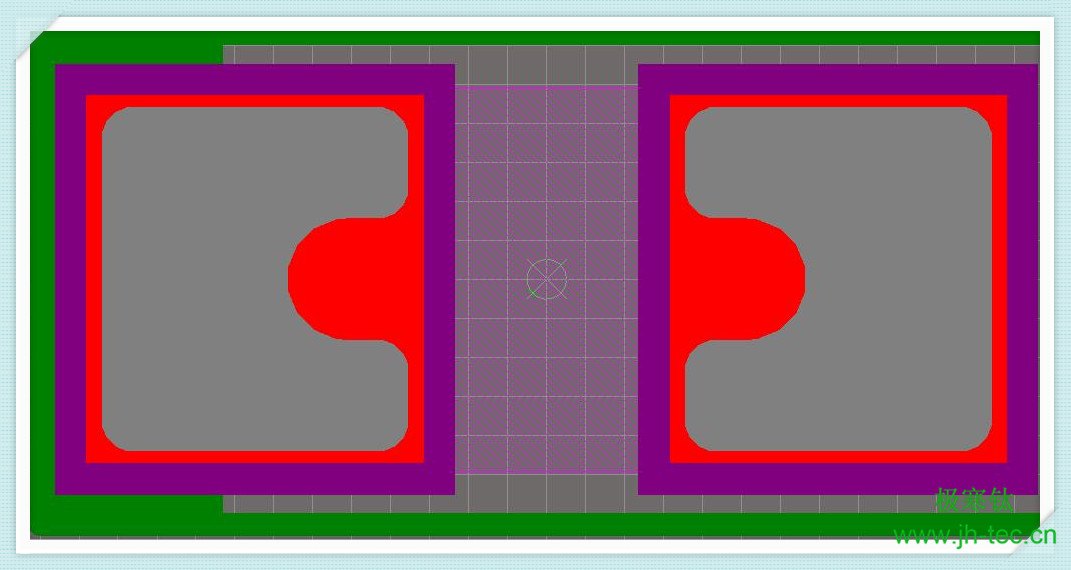

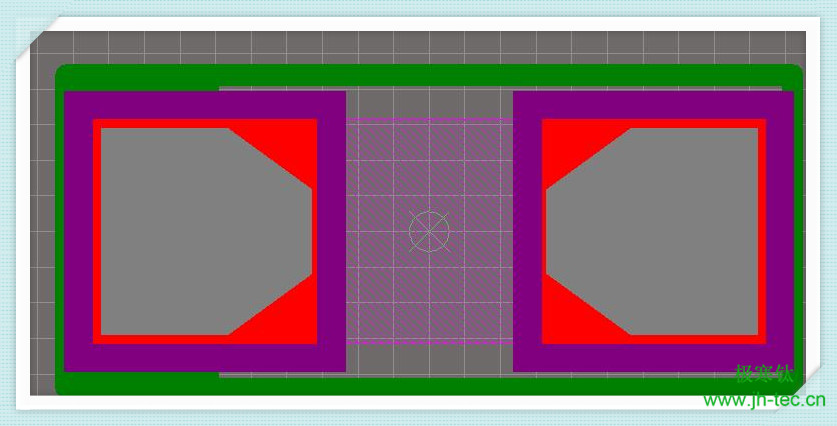

3.关于封装Top-Paste的设计注意事项

Paste层主要用于后期SMT开钢网所参考的层,很多朋友在设计封装的时候很少注意到该层,多数人在制作焊盘完成之后就默认Paste面积和焊盘一样,这样子看似没问题,但后期贴片生产却会带来诸多意想不到的麻烦。比如产生过多的锡珠、钢网孔过大导致引脚短路、锡融合不全等等,我们在设计过程中可以参照如下图所示,采用异性孔、半孔、大孔改多个小孔的方式来来减少这类现象的产生,大的焊盘一定要尽量控制钢网孔的大小,不然很容易出现锡融化不全所导致的短路现象。

【在产品选型阶段,关于器件封装的考虑】

1.能避免使用QFN就尽量避免

为何这么讲?QFN封装在量产SMT过程中容易出现引脚连锡的现象,钛叔在曾经参与过一款产品的量产,小批量(200套) SMT没出现任何问题,测试全部通过,但到了第二批生产(2000套),出现了大量(几十套)的连锡情况,这个概率是极其严重的,给生产带去了巨大麻烦,只有将2000全部重新焊接一遍,测试过程中还会因为短路损坏一些产品。 因此,如果能够选择QFP SOP封装替代前者就尽量选择。

【PCB设计过程中封装的注意项】

1.过孔的放置

焊盘上切忌放置过孔! 如果焊盘上放置了过孔,在SMT过程中,焊锡会通过过孔留下去,造成的结果就是虚焊! 有很多工程师在设计过程中不注重这个问题,因为他们大多数只会考虑走完线,手动焊接也不会影响,完事。

2.芯片或者模块下边要不要走线

在我们layout过程中常常会遇到这个问题,如果芯片下边有裸露的焊盘,钛叔是坚决不建议走线的;如果是新品下边没有焊盘,钛叔给出的建议能不走就尽量不走,原因是在我们调试过程中,如果大量走线从新品肚子下面过,一是不方便我们识别走线,第二也不方便后期调试,比如设计到飞线之类的,当然如果板子面积实在有限就另当别论了。为什么会提到模块呢,有些射频模块会焊接到我们设计的主板上,而这类型模块占有面积比较大,不走线是很难做到的,钛叔给出的建议还是能不走就不走,如果要走线,建议在该部分铺上一层丝印在盖油上,这样盖油层和丝印层量产隔离开,短路的风险也会大大降低。

3.之前钛叔使用过一个射频模块,需要将该模块焊接到底控制板上,该模块的GND引脚偏大,因此我封装也画的大,理所当然的将钢网孔也开的和封装面积一样,在手动刷锡膏的时候刷的量自然也较大,经过炉子焊接好之后上电即出现短路的情况,但是从外观上看不出一点问题,后来仔细分析原因就是由于模块GND引脚焊盘的锡膏量大,而引脚散热又强,导致锡膏融化不足,模块底部大量的锡将旁边管脚短路。因此,当板子上某个封装的某个引脚面积较大,且它所连铜皮面积也大时(如GND),在开钢网时候就一定要注意将该引脚的孔开小些,避免由于引脚面积大散热快,造成过流焊的时候,锡膏融化不够而引起与旁管脚短路的情况。

待续…

后续钛叔还将不断更新该篇博客,将实际设计、生产、调试过程中发现的诸多有关封装的问题给大家分享出来,希望对大家有所帮助。

参考库:

链接:https://pan.baidu.com/s/18A6MK53jEh6X0LBppS8Xsw

提取码:a2f5